JETIR.ORG

ISSN: 2349-5162 | ESTD Year: 2014 | Monthly Issue

## JOURNAL OF EMERGING TECHNOLOGIES AND INNOVATIVE RESEARCH (JETIR)

An International Scholarly Open Access, Peer-reviewed, Refereed Journal

# Three-phase improved cascaded multilevel inverter with multi-carrier sinusoidal pulse width modulation with variable frequency technique for THD reduction

Dr.J.Upendar<sup>1</sup>, V.Aditya Yadav<sup>2</sup>, S.Sreenu<sup>3</sup>, Bogimi Sirisha<sup>4</sup>

<sup>1</sup>Assistant Professor, <sup>2</sup>PG Students, <sup>3</sup>Research Scholar, <sup>4</sup>Associate Professor,

<sup>1,2,3,4</sup>Department of Electrical Engineering,

1,2,3,4University College of Engineering, Osmania University, Hyderabad, Telangana, India

Abstract: This research work focuses on Three phase improved a cascaded multilevel inverter with multi-carrier sinusoidal pulse width modulation using a variable frequency approach and an active filter. MLI came out as a vital converter in industrial drives to regulate speed and to lower THD level for high power medium voltage applications. Due to harmonic content, traditional inverter-fed induction motor drives have poor voltage and current quality, resulting in energy losses. A new topology of cascaded multilevel inverter with fewer switches is introduced to reduce THD and deliver higher power quality supply. It only requires nine semiconductor devices, whereas conventional topology requires twenty for the same 11-level output. The number of switches need for this configuration is {(n-1)/2} +4 for n level voltage output. Harmonic content is decreased using an active LPF filter. With resistance and an asynchronous motor as load, and FFT analysis, eleven level MLI with active LPF filter and seven level MLI with active filter are simulated. With and without a filter, total harmonic distortion of a voltage waveform is investigated.

### Index Terms- Multilevel Inverter, Multi-carrier sinusoidal PWM, Active filter

### I. Introduction

Various manufacturing companies require high power rating converters in recent years. Few medium power rating motor drives and utility applications need medium voltage and medium power level. For a high voltage level power grid, it is not recommended to transmit AC power for longer distances in order to minimize the losses in transmission lines. There is also frequency stability problem in AC transmission. So, HVDC transmission system came into existence. The power generated at power plants is converted to DC through rectifiers and the filtered ripple-free DC is fed to HVDC power grid and at the load centers, it is converted back to AC as per the load requirement. The THD content in this AC supply has to be as low as possible. To achieve this in high power and medium power levels, a multi modular inverter structure has been introduced as an alternative for conventional two-level inverter which is used at low power requirement. A MMI not only matches high power ratings, but also allows us to use Nonconventional energy sources. Non-conventional sources such as photovoltaic panels, wind turbines, and fuel cells can be easily interfaced to medium and high-power applications through multilevel inverters.

Multi-modular converters were first proposed in 1975, and more advancements in this field of power conversion are in the works. With the three-level inverter, the word "multilevel" was coined. Many other multilayer inverter topologies were developed later. The fundamental goal of a multilayer converter is to generate high power... which is accomplished by combining a series of power semiconductor switches with a large number of low-level voltage DC sources to complete the power conversion operation and generate a staircase voltage waveform. Capacitors, batteries, and a variety of other non-conventional energy-controlled voltage sources can all be used as DC voltage regulators. The complete high voltage in the output is created by standardized switching in addition to commutation of these power semiconductor switches that are correlated to various DC voltage sources.

### II. PROPOSED MODEL

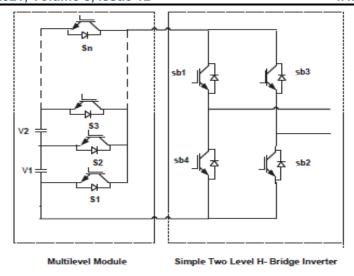

The block diagram of proposed model is in following figure 1, In this structure, switches Sb1, Sb2, Sb3, Sb4 are employed for changing the polarity of staircase DC input while staircase DC is produced using Switches S1, S2, S3.

Three switches are active at the same time to produce any output voltage level. Only one switch is activated by the multi-level module, while the other two are activated by the H-bridge inverter. The number of switches required for this architecture is  $\{(m-1)/2\}+4$  for any output level, where m is the inverter's output level.

Figure 1. Proposed model Block diagram

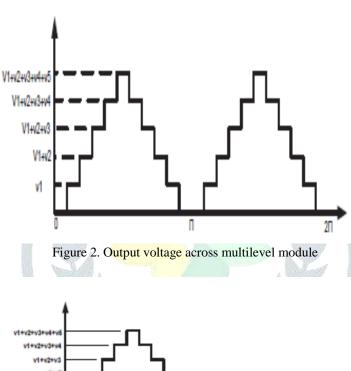

V1+V2+V3+V4

V1+V2+V3+V4

V1+V2+V3

V1+V2

V1

V1-V2

V1

-V1-V2

-V1-V2-V3

-V1-V2-V3-V4-V5

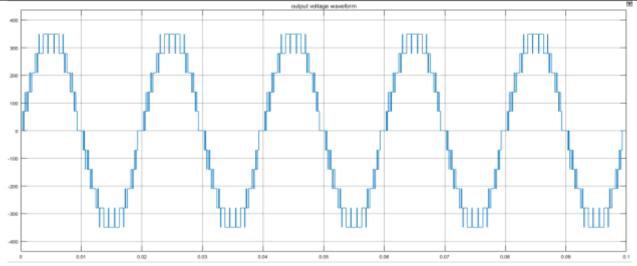

Figure 3. Output voltage across H-bridge inverter

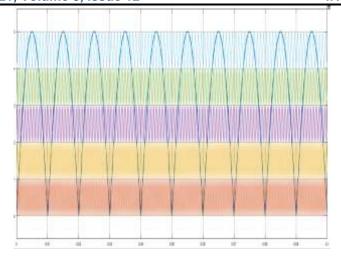

## III. MULTICARRIER SINUSOIDAL PWM

The technique used is not like a conventional PWM technique. In this technique only positive half of the sine reference wave compared with level shifted multi carrier triangular waves which are having different frequencies are compared and the output is high when the sine reference wave is higher the triangular carrier wave and the output will be low when the sine reference wave is less the triangular carrier wave. The generated pulses are given to corresponding switches. Moreover the carrier waves are present only above zero level, there are no triangular carrier waves present below zero since the desired output at multilevel module is stair-cased positive wave form and the output is inverted at Two level output module. The simple H-bridge switches are having the frequency equal to required output frequency.

When observed above PWM techniques this is quite different in operation. This multi-carrier PWM techniques are simple yet gives better results and more predominant for multilevel inverters. Whereas Space -Vector Pulse width modulating technique is robust but complex and it becomes very difficult in implementation when comes higher voltages levels.

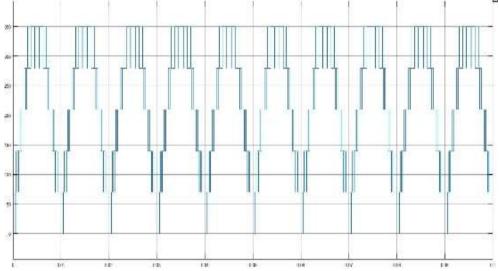

Figure 4.Multi-carrier Sinusoidal PWM with variable frequency for proposed model

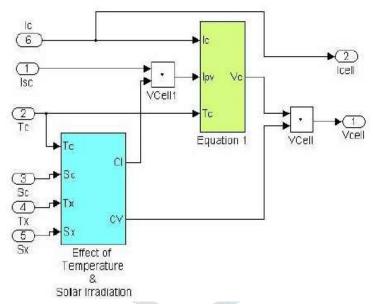

### IV. PV ARRAY FOR MULTILEVEL INVERTERS

PV arrays are still widely seen as an expensive option when compared to existing utility-generated electricity from fossil fuels. After spending so much money on a non-conventional energy system, the consumer usually wants to run the PV array at its highest energy conversion output, utilizing all of the array's available solar power. Due to the variable nature of the solar power generated as a result of unforeseen and abrupt changes in climatic conditions, which could modify the solar insolation level and as well as the PV cell functioning temperature, the system of electricity powered by solar arrays requires special design parameters.

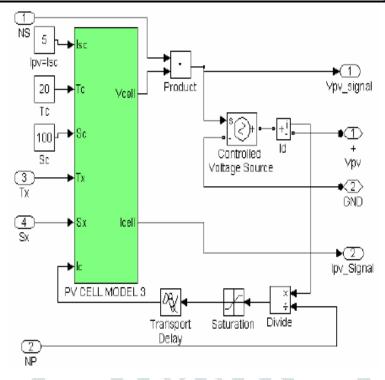

Figure 5. Modelling stage-1

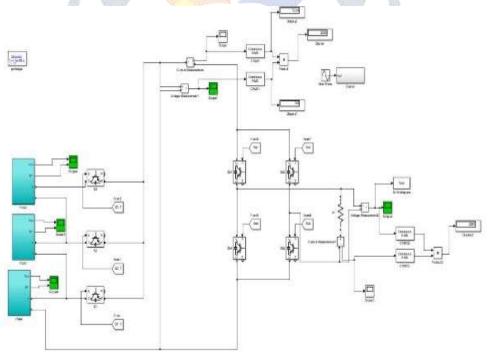

Figure 6. Modeling stage-2

### V. MATLAB SIMULATION RESULTS

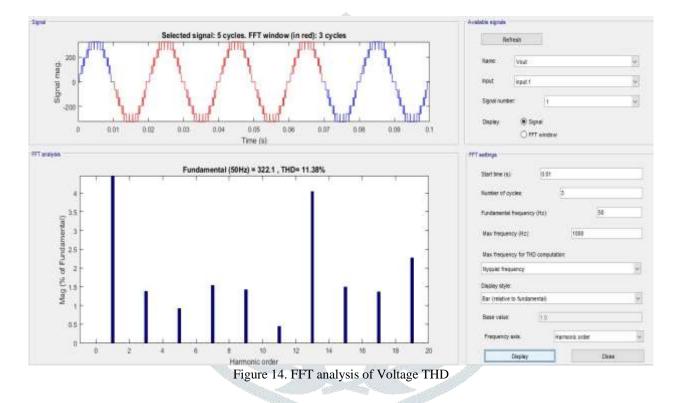

Simulation results of Total Harmonic Distortion (**THD**) of Seven -level and Eleven level Inverter are included so that THD difference of different levels is analyzed in MATLAB-R2016. Multi carrier sinusoidal pulse width modulation with variable frequency technique is applied for Seven and Eleven level inverter and the result of THD are compared. As the level of the inverter increases, generally, the harmonic content reduces, the waveform approaches nearer to sine wave as the level increases. So, a Eleven-Level inverter will have low THD than a Seven-Level inverter.

Figure 7. Seven level MLI

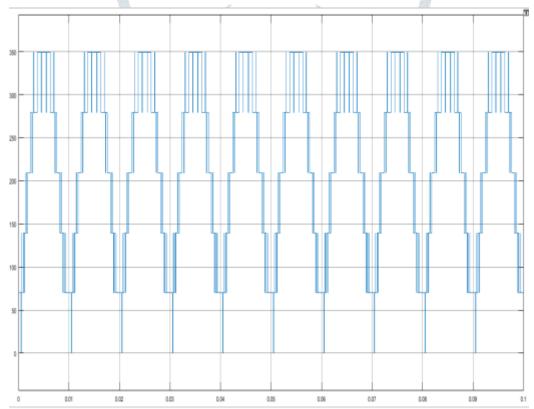

Figure 8.Output Voltage across Multilevel Module

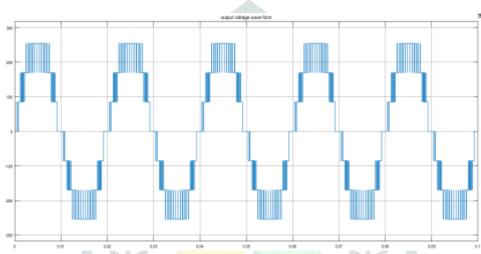

Figure 9. Output Voltage across H-bridge

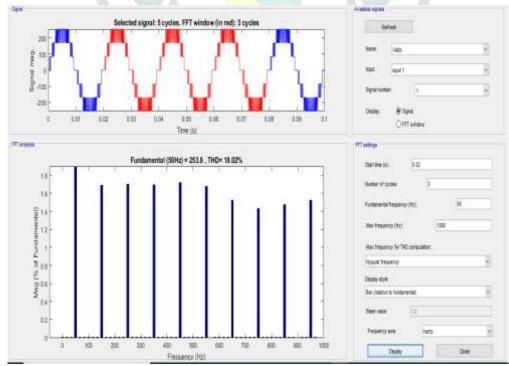

Figure 10. FFT analysis of voltage waveform of seven level MLI

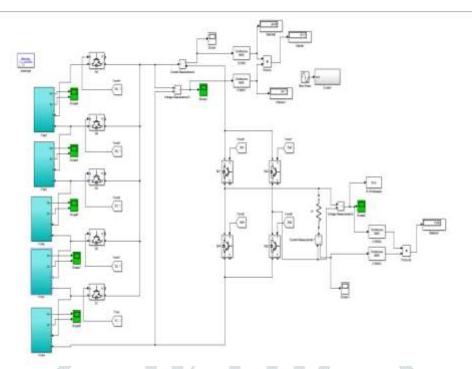

Figure 11. Eleven level MLI

Figure 12. Output Voltage across Multilevel module

Figure 13. Output Voltage across H-bridge inverter

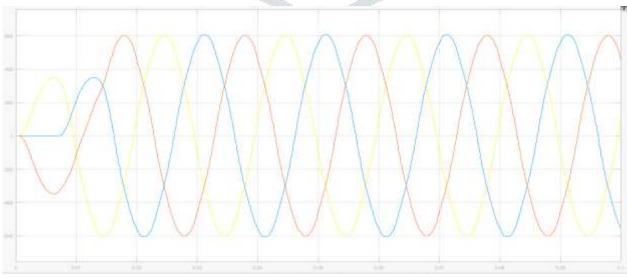

Figure 15. Three phase line voltage with active filter

Table 1. THD comparisons(modulation index =1)

| Voltage level              | THD (without filter) | THD (with filter) |

|----------------------------|----------------------|-------------------|

| Seven level phase voltage  | 18.02%               | 1.73%             |

| Seven level line voltage   | 14.89%               | 0.97%             |

| Eleven-level phase voltage | 11.38%               | 2.12%             |

| Eleven level line voltage  | 8.83%                | 1.45%             |

Table.2.THD comparisons (modulation index =0.9)

| Voltage level              | THD (without filter) | THD (with filter) |

|----------------------------|----------------------|-------------------|

| Seven level phase voltage  | 22.01%               | 1.73%             |

| Seven level line voltage   | 18.01%               | 1.00%             |

| Eleven-level phase voltage | 13.15%               | 1.90%             |

| Eleven level line voltage  | 11.06%               | 1.19%             |

### VII. CONCLUSION

Simulation models have been built for seven and Eleven-level inverters using the SIMULINK in MATLAB-R2016 to synthesize single-phase and three-phase voltages using the idea of stair-case voltage waveform construction with MCSPWMVF technique. To have a better overview of the behavior of different multi-level inverters, a comparison table detailing THD is provided for the ease of understanding the advantages of multi-level inverters and also the role of MCSPWMVF in reduction of THD further in low level inverters that requires less number of DC sources, switches and auxiliary driving circuits. Thus, the construction becomes less complex and more economical.

### REFERENCES

- [1] Arman, M.F., and Darwish, M.K., 2009, "Critical Review of Cascaded H-Bridge Multilevel Inverter Topologies," International Review of Electrical Engineering, 4(5), pp. 730-743.

- [2] Angulo, M., Lezana, P., Kouro, S., Rodriguez, J., and Wu, B., 2007, "Level-Shifted PWM for Cascaded Multilevel Inverters with Even Power Distribution," Proc. IEEE Power Electron. Spec. Conf., pp. 2373–2378.

- [3] Baker, R. H., and Bannister, L. H., 1975, "Electric Power Converter," U.S. Patent 3 867 643.

- [4] Brahim, L.B., and Tadakuma, S., 2006, "A Novel Multilevel Carrier- Based PWM Control Method for GTO Inverter in Low Index Modulation Region," IEEE Trans. Ind. Applicat., 42(1), pp.121-127.

- [5] Bhagwat, P. M., and Stefanovic, V.R., 1983, "Generalized Structure of a Multilevel PWM Inverter," IEEE Trans. Ind. Applicat., 19(IA), pp. 1057–1069.

- [6] Busquets-Monge, S., Alepuz, S., Bordonau, J., and Peracaula, J., 2008, "Voltage Balancing Control of Diode Clamped Multilevel Converters with Passive Front-Ends," IEEE Trans. Power Electron., 23(4), pp. 1751–1758.

- [7] Bowes, S.R., and Holliday, D., 2007, "Optimal Regular-Sampled PWM Inverter Control Techniques," IEEE Trans. Ind. Electron., 54(3), pp. 1547–1559.

- [8] Boost M.A., and Ziogas, P.D., 1988, "State-of-the-art Carrier PWM Techniques: A Critical Evaluation," IEEE Trans. Ind. Appl., 24(2), pp. 271–280. 135

- [9] Bansal S.C., and Rao, U.M., 1978, "Evaluation of PWM Inverter Schemes," Proc. Inst. Elect. Eng., 125(4), pp. 328-334.

- [10] Corzine, K.A, and Familiant, Y., 2002, "A New Cascaded Multilevel H-Bridge Drive," IEEE Trans. Power Electron., 17(1), pp.125-131.

- [11] Corzine, K.A., Wielebski, M.W., Peng, F.Z., and Wang, J., 2004, "Control of Cascaded Multilevel Inverters," IEEE Trans. Power Electron., 19(3), pp.732-738.

- [12] Carrara, G., Gardella, S., Marchesoni, M., Salutari, R., and Sciutto, G., 1992, "A New Multilevel PWM Method: A Theoretical Analysis,"IEEE Trans.Power Electron., 7(3), pp. 497-505.

- [13] D. Narsale and S. S. Dhamse, "Three Phase Improved Cascaded Multilevel Inverter Fed Induction Motor Drives For THD Reduction," 2018 Second International Conference on Green Computing and Internet of Things (ICGCIoT), Bangalore, India, 2018, pp. 84-88, doi: 10.1109/ICGCIoT.2018.8753045.